马上就迎来大学生涯中最后一次期末考试了,在这里我把《微机原理与接口》课程的知识按照张春芳老师给的提纲进行了梳理。下面正文是文字的形式,文末还有思维导图的形式一并共享给大家,期待和大家一起考出好成绩。

说明

按照老师给的提纲顺序,我对每一个点进行了梳理,覆盖率98%,并在每一个点后面附上了课本出处页码,以方便查阅课本原文。有的点没有达到100%覆盖,是我复习过程中遇到的问题,我会在向老师求教后及时更新。

这一份知识梳理是我在刚刚过去的2天里,利用了20多个小时的时间,翻阅课本,查阅PPT后逐字手敲的结果,可能其中会有疏漏,还请见谅!

Chapter 1-3

1.二进制数据类型、表示、范围及其转换 P11-13

- 定点整数

- 无符号整数:只表达0和正整数

- 8位范围:0-255

- N位范围:0~2^N-1

- 有符号数:占用机器数的最高位当符号位,0表示正,1表示负

- 无符号整数:只表达0和正整数

- 原码和反码

- 补码

- 原反补码的转换

- 逻辑地址:“段地址:偏移地址”的形式表示的地址

- 物理地址:将逻辑地址中的段地址左移二进制4位,加上偏移地址20位所组成的地址

- 转换:段地址×16+偏移地址=物理地址(可以理解为段地址末尾补一个零)

3.段地址、偏移地址的寄存器表示及计算 P23-24

- 代码段 - CS:IP

- 堆栈段 - SS:SP

- 数据段 - 存放当前运行程序所用的数据。DS存放数据段的段地址,存储器中的操作数的偏移地址则由各种主存寻址方式得到,称之为有效地址EA

- 附加段 - 是附加的数据段,也用于数据的保存。

- 使用BP基址指针寄存器访问主存,则默认是SS段,同时也允许段超越。

4.汇编语言语句的格式 P25 P54-56

- 执行性语句

- 格式 - 标号: 处理器指令助记符 操作数, 操作数 ;注释

- 说明性语句

- 格式 - 名字 伪指令助记符 参数,参数,······ ;注释

- 标号与名字:是用户自定义的符合汇编程序语法的标识符

- 标识符

- 最多由31个字母、数字及规定的特殊符号(_、$、?、@)组成

- 不能以字母开头

- 不能是汇编程序采用的保留字

- 标识符

- 助记符:是帮助记忆的符号,反映指令的功能

- 操作数和参数

- 立即数寻址:用常量表达具体的数值

- 寄存器寻址:用寄存器名表示其中的内容

- 操作数可放在:AH/AL/BH/BL/CH/CL/DH/DL/AX/BX/CX/DX/SI/DI/BP/SP

- 还可以放在段寄存器中:CS/DS/SS/ES

- 存储器寻址:用存储器地址代表保存的数据

- 直接寻址

- 其默认段地址在DS段存储器中,可以使用段超越前缀来改变例:MOV AX,[2000H]

- 寄存器间接寻址

- 在8088/8086中寄存器可以是BX/BP/SI/DI例:MOV AX,BX

- 寄存器相对寻址

- 寄存器可以是BX/SI/DI,默认是数据段DS

- 也可以是BP,默认是堆栈段SS

- 都可用段超越前缀改变

- 例:MOV AX,[SI + 06H]

- 基址变址寻址

- BX或BP + SI或DI = EA(有效地址)

- 例:MOV AX,[BX + SI] 或 MOV AX,[BX] [SI]

- 都可用段超越前缀改变

- 相对基址变址寻址

- 直接寻址

- 数据传送类指令

- 通用数据传送指令 - 传送指令MOV

- 功能:把一个字节或字的操作数从源地址传送至目的地址

- 格式:见P29

- 不影响任何标志位

- 目的操作数和源操作数必须类型一致,否则为非法指令

- 堆栈操作指令 - PUSH、POP

- 功能:堆栈是一个“先进后出”的主存区域,使用SS段寄存器记录段地址;堆栈只有一个出口,即当前栈顶,用堆栈指针寄存器SP指定栈顶的偏移地址。

- 入栈指令PUSH会使堆栈指针SP减2,出站指令POP会使堆栈指针SP加2。

- 格式:见P31

- 不影响任何标志位

- 标志操作指令

- 可以直接读写标志寄存器的内容以及可以直接改变CF、DF、IF标志的状态的指令

- 地址传送指令 - LEA

- 功能:将存储器操作数的有效地址(段内偏移地址)传送至16位通用寄存器中

- 格式:见P33

- 不影响任何标志位

- 通用数据传送指令 - 传送指令MOV

- 算术运算类指令

- 加法和减法指令 - 加法指令ADD、ADC、INC,减法指令SUB、SBB、DEC、NEG和CMP

- 功能:它们分别执行字或字节的加法和减法运算

- 格式:见P33

- 除INC和DEC不影响CF标志外,其他按定义影响全部状态标志位

- 符号扩展指令

- CBW ;字节转换为字:AL符号扩展成AX

- CWD ;字转换为双字:AX符号扩展成DX

- 乘法和除法指令

- 乘法指令

- MUL ;无符号数

- IMUL ;有符号数

- 除法指令

- DIV ;无符号数

- IDIV ;有符号数

- 乘法指令

- 加法和减法指令 - 加法指令ADD、ADC、INC,减法指令SUB、SBB、DEC、NEG和CMP

- 位操作类指令

- 逻辑运算指令 - AND、OR、XOR、TEST、NOT

- 功能、格式:见P37

- AND(与)/OR(或)/XOR(异或)/TEST(测试)会使CF、OF都清零,其他标志位按定义影响。NOT(非)不影响任何标志位。

- 逻辑运算指令 - AND、OR、XOR、TEST、NOT

- 串操作类指令

- 控制转移类指令

- 条件转移指令

- JZ/JNZ:利用零标志ZF,分别判断结果是0(相等)还是非0(不等)

- JS/JNS:利用符号标志SF,分别判断结果是负还是正

- JO/JNO:利用溢出标志OF,分别判断结果是溢出还是没有溢出

- JC/JNC:利用进位标志CF,判断结果是有进位(1)还是无进位(0)

- 循环指令

- LOOP ;CX←CX-1 ;若CX≠0,转移

- 循环次数必须放在CX中

- JNZ ;不为0转移

- JCXZ ;为0循环:CX=0,转移

- LOOP ;CX←CX-1 ;若CX≠0,转移

- 中断指令

- 21号中断

- INT 21H ;屏幕显示

- 21号中断

- 条件转移指令

- 处理器控制类指令

7.汇编伪指令的类型、格式及应用 P61

- DB:字节(Byte)类型,分配一个或多个字节单元

- DW:字(Word)类型,分配一个或多个字单元,每个数据是字量、16位数据

- DD:双字(Dword)类型,分配一个或多个双字单元,每个数据是双字量、32位数据

8.汇编语言编程的上机过程

- 用编辑器编辑代码后保存为汇编源文件(.asm)→经过编译得到目标文件(.obj)→经过连接生成可执行文件(.exe)

9.汇编语言程序段的阅读、源程序的编写 P61-74

CHAPTER 4-5

1.总线类型及特点 P94-95

- ALE - 高电平有效

- IO/-M - 高低均有效,高电平表示CPU访问I/O接口,低电平表示CPU访问存储器

- -WR - 低电平有效,写控制

- -RD - 低电平有效,读控制

3.8086/8088功能结构和存储器结构 P136-137

4.8086/8088工作模式的配置结构:3:8地址译码器、地址锁存器类型和应用 P99-107

- 最小模式--即系统中只有8086(或8088)一个微处理器。最小模式是单处理器系统。系统中所需要的控制信号全部由8086(或8088)CPU本身直接提供

- 最大模式--系统中有两个或两个以上的微处理器,即除了主处理器8086(或8088)以外,还有协处理器(8087算术协处理器或8089 输入/输出协处理器)。最大模式可构成多处理器系统,系统中所需要的控制信号由总线控制器8288提供

5.8086/8088系统总线的类型 P107-111

6.存储器的类型、特点及典型芯片 P113-129

- 静态RAM(SRAM) 6116

- 动态RAM(DRAM) 4164

9.中断类型及特点 P159-160

- 除法错中断

- 指令中断

- 单步中断

11.中断过程 P152-154

Chapter 6-12

1.I/O接口、端口的概念、编址方法 P140-143

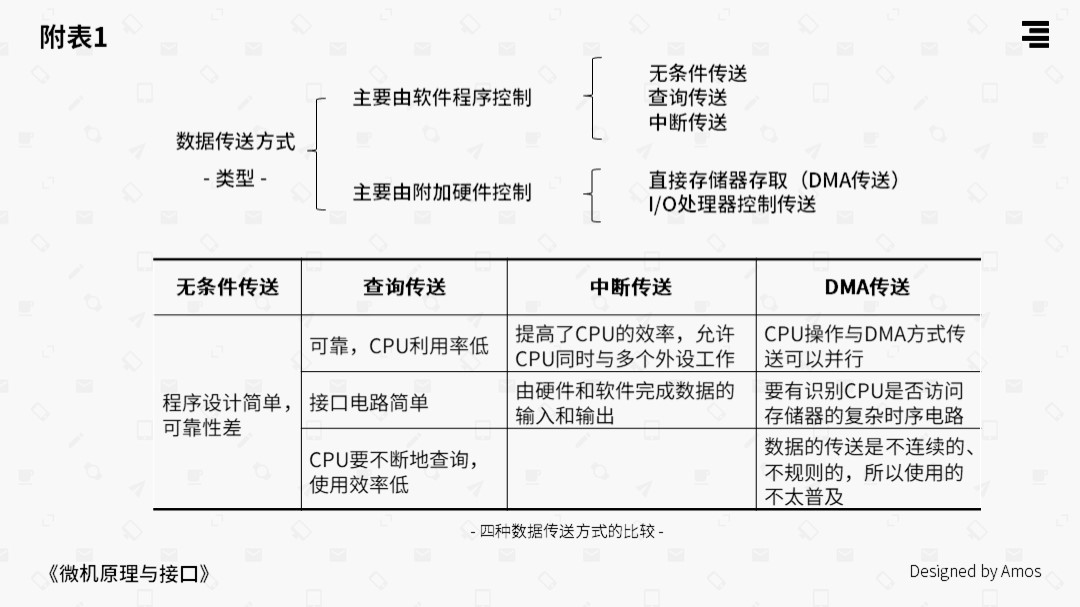

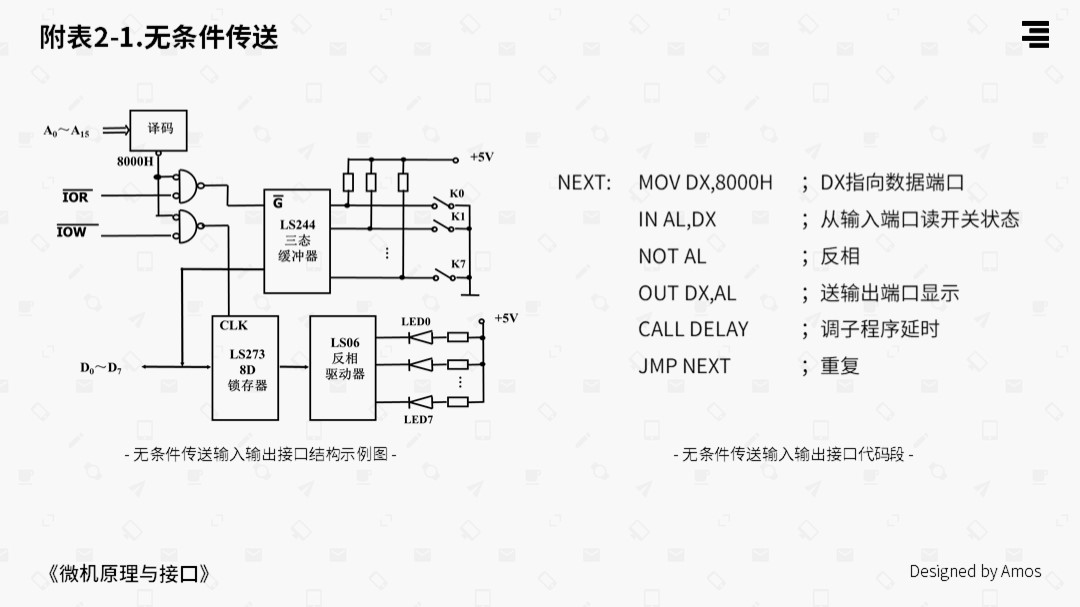

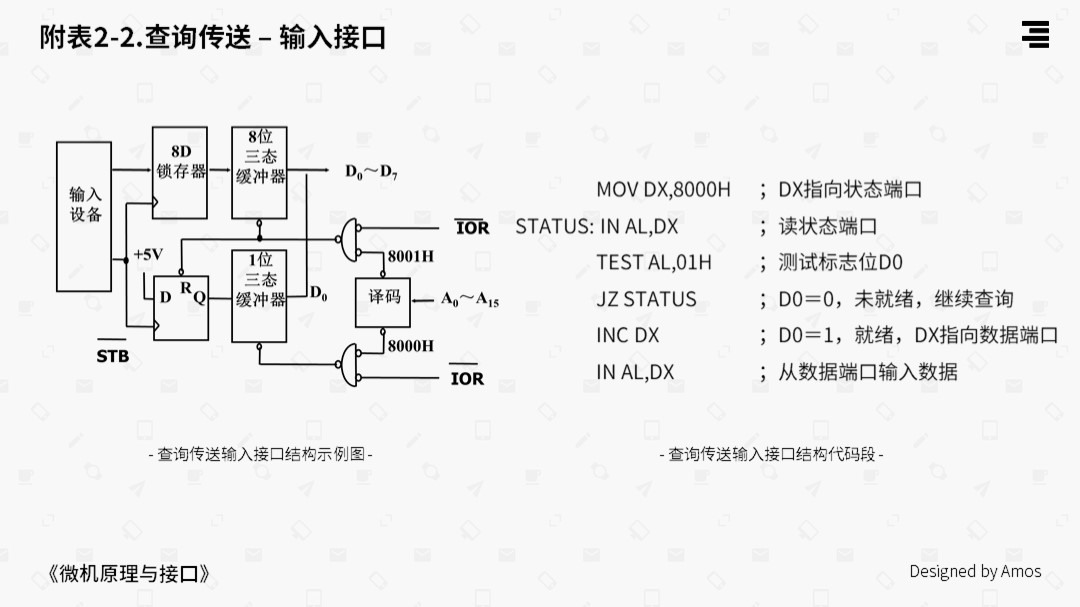

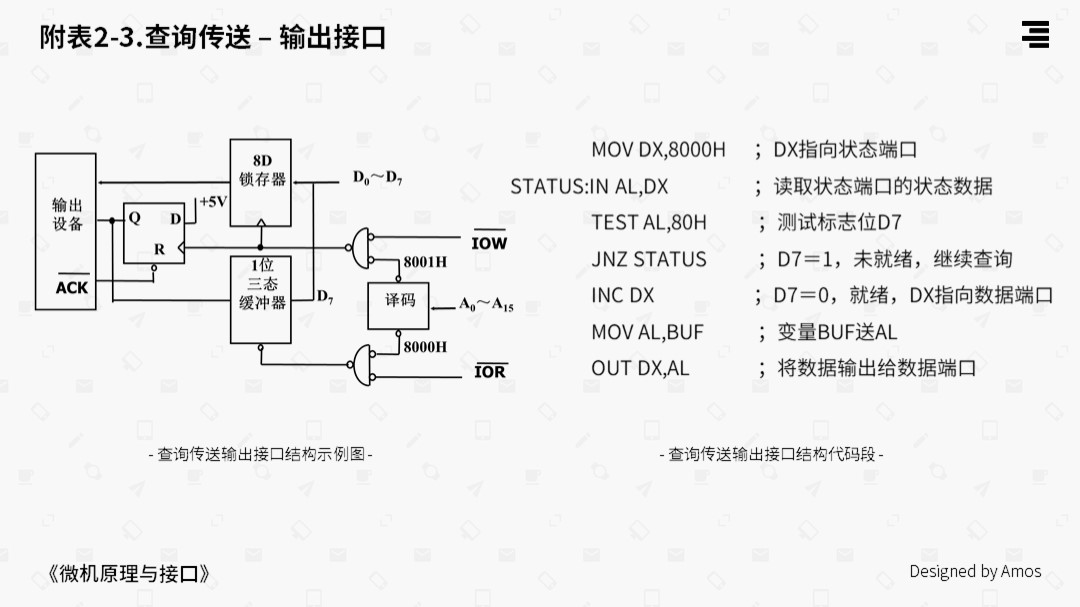

3.无条件传送、查询传送的原理、结构和程序段 P146-152

- 见附表2-1、2-2、2-3

4.8259功能、结构、引脚 P164-166

功能:管理Intel 8080/8085和Intel 8086/8088微处理器的可屏蔽中断

- 一片8259A可以管理8级中断,可扩展至64级

- 每一级中断都可单独被屏蔽或允许

- 在中断响应周期,可提供相应的中断向量信号

- 有多种工作方式,可以通过编程来选择

结构及引脚

功能

- 具有三个独立的16位减法计数器

- 每个计数器可按二进制或十进制计数

- 每个计数器的计数速率可达2MHZ

- 每个计数器有六种工作方式

- 全部输入输出都与TTL电平兼容

结构与引脚

- 数据总线缓冲器

- 8位双向3态缓冲器,CPU与8253数据联络通道

- 读写控制电路

- CS—片选信号RD—读8253

- WR—写入8253

- A0、A1—计数通道地址选择

- 控制字寄存器

- 8位寄存器,在8253初始化时,由CPU写入控制字,以决定计数通道的工作方式

- 计数器通道

- 计数器0、计数器1、计数器2独立16位减法计数器,计数值可写入或读出

- 引线

- CLK—时钟脉冲输入线

- GATE—门控信号输入,为低时禁止计数器计数

- OUT—计数/定时输出,当计数到0时输出信号

- A0、A1—通道地址选择00—计数器0;01—计数器1;10—计数器2;11—控制字寄存器

- 数据总线缓冲器

工作方式

- 方式0:计数结束中断

- 方式1:可编程单稳脉冲

- 方式2:频率发生器(分频器)

- 方式3:方波发生器

- 方式4:软件触发选通信号

- 方式5:硬件触发选通信号

初值计算

- 见课本P187

控制字

- 控制字的作用是决定8253各计数器工作方式;控制字寄存器实际上是3个,分别控制三个计数器,但它们的端口地址相同。

- D7、D6:计数器选择

- 00 - 计数器0

- 01 - 计数器1

- 10 - 计数器2

- 11 - 非法

- D5、D4:读写格式

- 00 - 计数器锁存

- 01 - 只读写计数器的低8位,高8位自动为0

- 10 - 只读写计数器高8位,低8位自动为0

- 11 - 先读写计数器低8位,再读写高8位

- D3D2D1:计数器工作方式

- 000 - 方式0

- 001 - 方式1

- ×10 - 方式2

- ×11 - 方式3

- 100 - 方式4

- 101 - 方式5

- D0:计数数制,决定计数器按二进制计数或BCD码(十进制)计数。

- 0 - 二进制

- 1 - BCD码(十进制)

初始化编程

有4个独立DMA通道,每个通道均可独立传送数据

每个通道DMA请求都可分别允许和禁止

每个通道均有64KB寻址和计数能力(16位地址寻址能力)

有4种DMA传送方式,分别为单字节传送、数据块传送、请求传送和级联传送方式

需要更多数据传送通道可把8237A级联

7.8255功能、结构、引脚、工作方式、控制字及连接打印机的应用 P210-221

功能

- 一个并行输入、输出的LSI芯片,多功能的I/O器件,可作为CPU总线与外围的接口

- 具有24个可编程设置的I/O口,即3组8位的I/O口为PA口,PB口和PC口

结构与引脚

- RESET:复位输入线,当该输入端处于高电平时,所有内部寄存器(包括控制寄存器)均被清除,所有I/O口均被置成输入方式

- CS:芯片选择信号线,当这个输入引脚为低电平时,即/CS=0时,表示芯片被选中,允许8255与CPU进行通讯;/CS=1时,8255无法与CPU做数据传输

- RD:读信号线,当这个输入引脚为低跳变沿时,即/RD产生一个低脉冲且/CS=0时,允许8255通过数据总线向CPU发送数据或状态信息,即CPU从8255读取信息或数据

- WR:写入信号,当这个输入引脚为低跳变沿时,即/WR产生一个低脉冲且/CS=0时,允许CPU将数据或控制字写入8255

- D0~D7:三态双向数据总线,8255与CPU数据传送的通道,当CPU 执行输入输出指令时,通过它实现8位数据的读/写操作,控制字和状态信息也通过数据总线传送

工作方式

- 方式0:基本输入输出方式

- 方式1:选通输入输出方式

- 方式2:双向选通输入输出方式

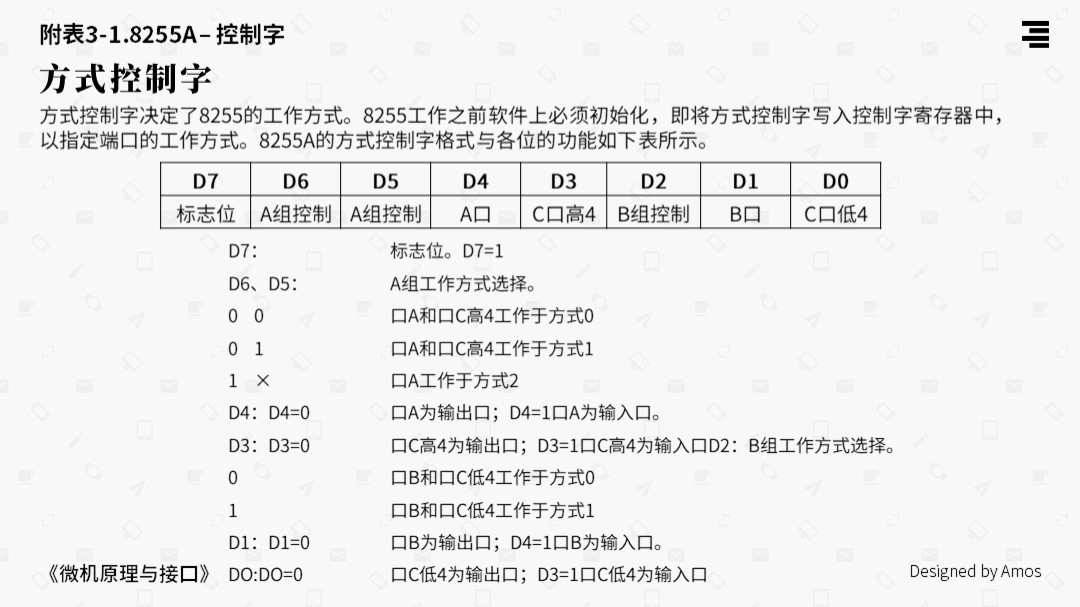

控制字

方式控制字,详见附表3-1

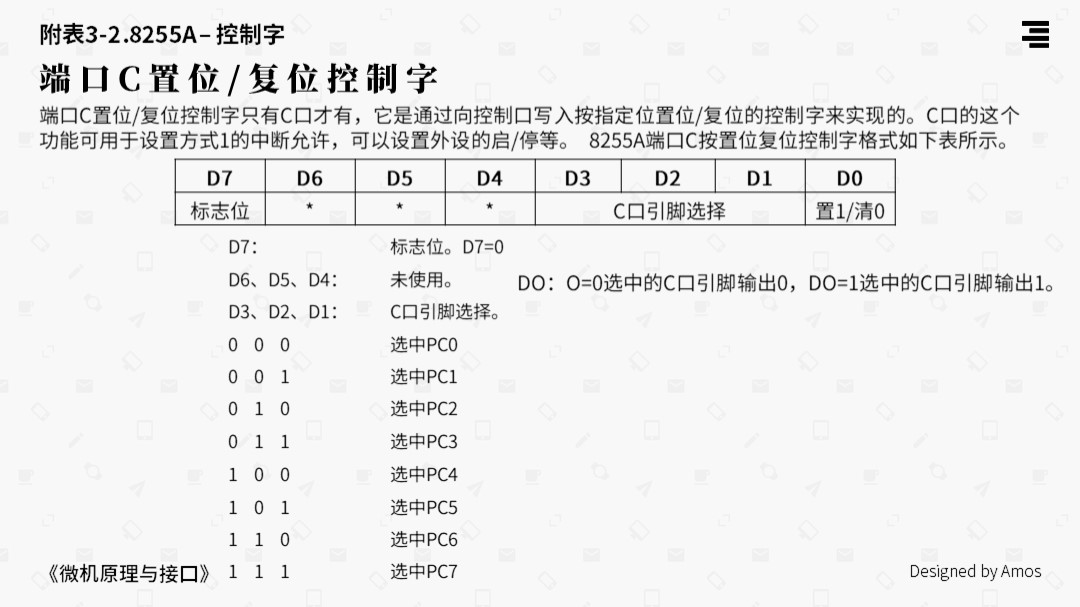

端口C置位/复位控制字,详见附表3-2

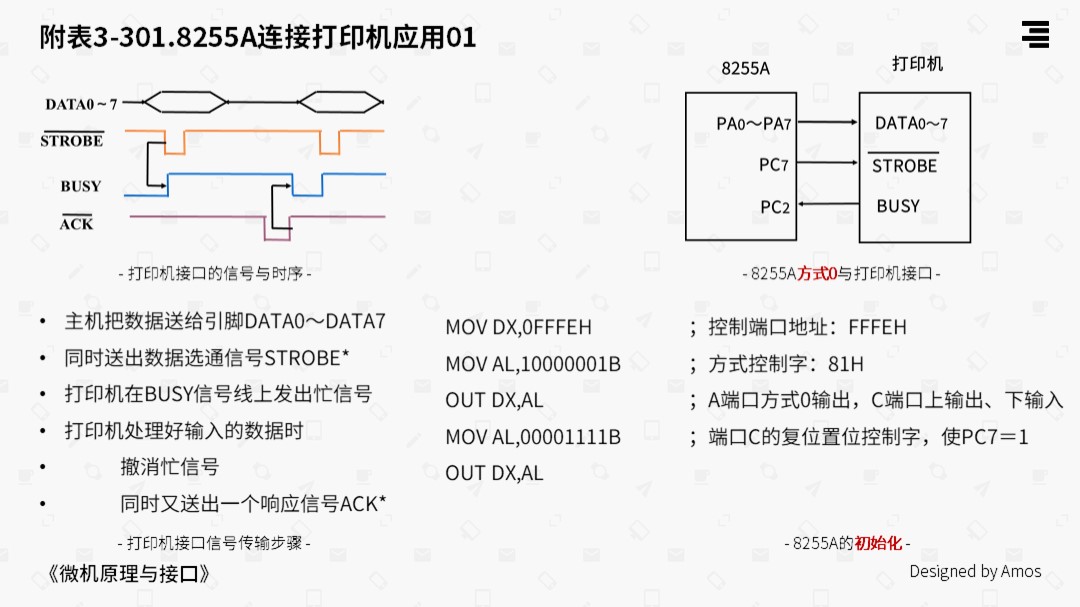

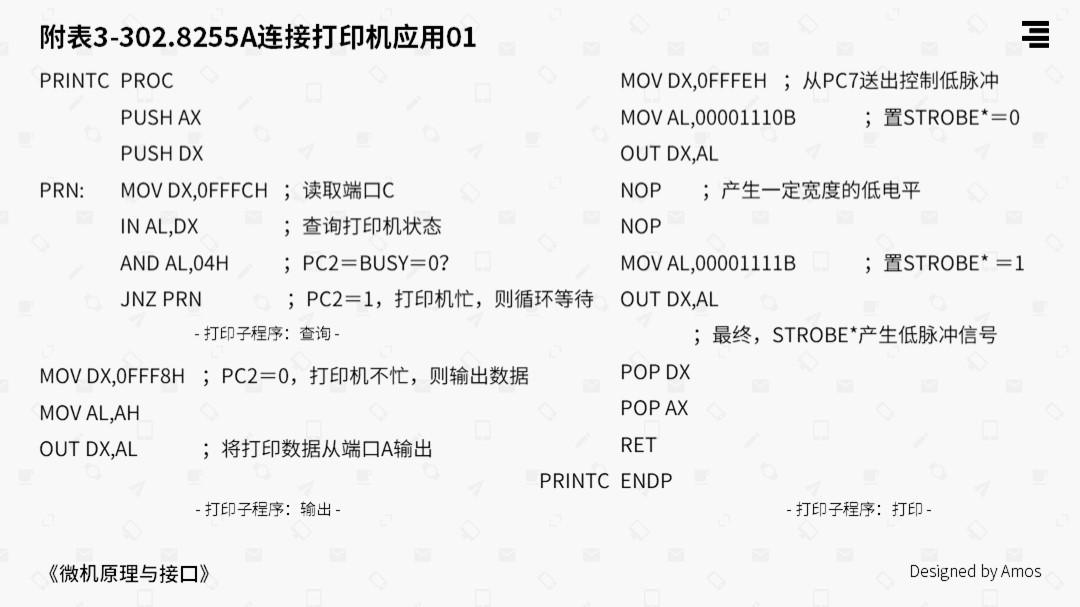

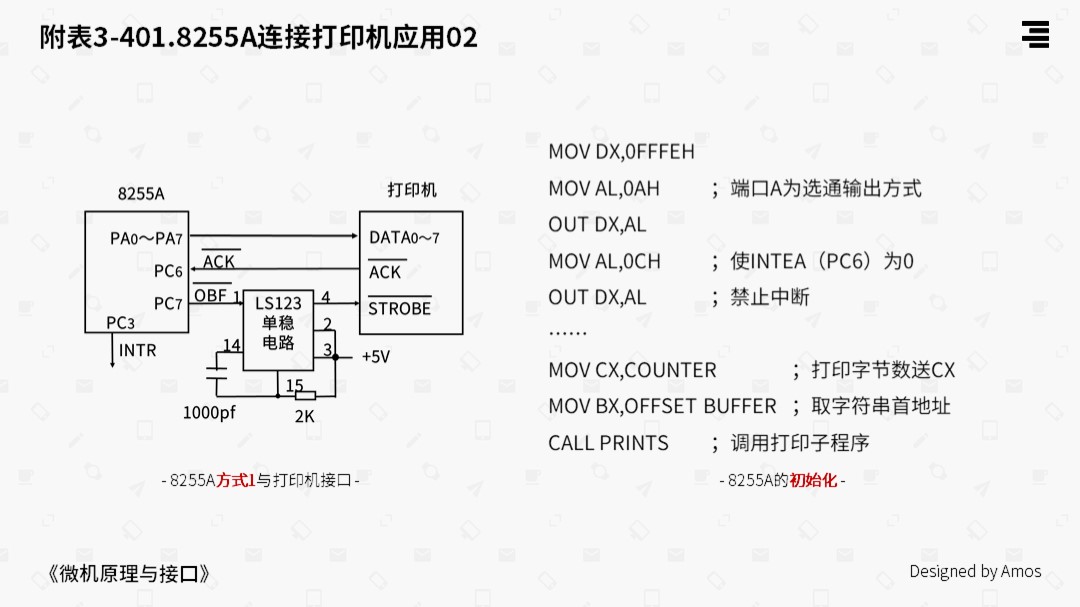

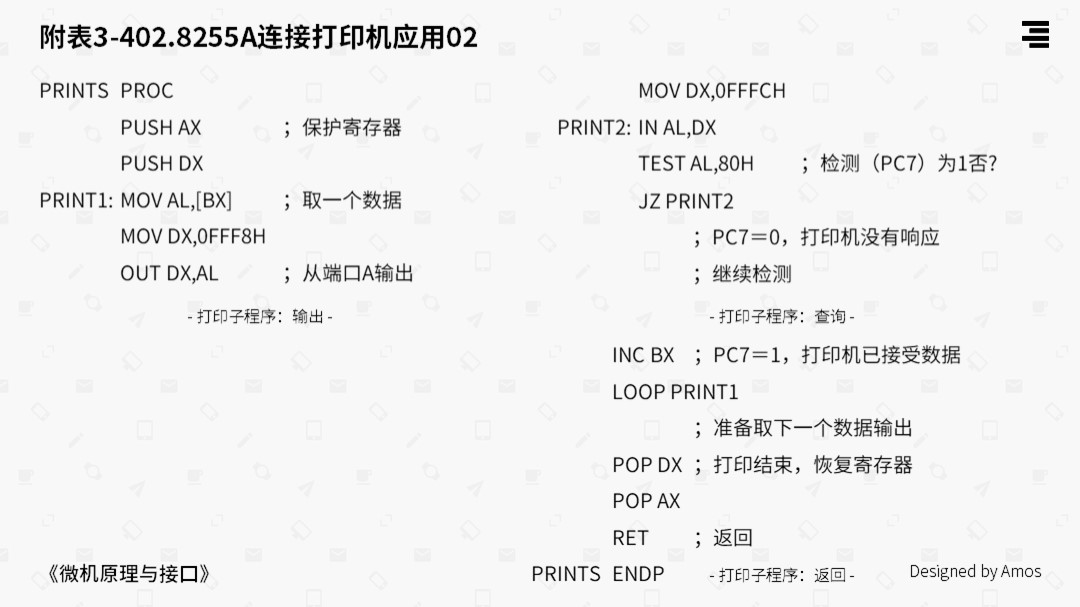

连接打印机应用

功能

- 实现了起止式串行异步通信协议,支持全双工通信

- 通信字符可选字数据位为5~8位,停止位1、1.5或2位

- 可进行奇偶校验,具有奇偶、帧、溢出错误的检测电路

波特率

- 在串行通信中,用 “ 波特率” 来描述数据的传输速率。所谓波特率,即每秒钟传送的二进制位数,其单位为 bps ( bits per second )。它是衡量串行数据速度快慢的重要指标

波特因子